同步操作将从 FlameAI/SIGer 强制同步,此操作会覆盖自 Fork 仓库以来所做的任何修改,且无法恢复!!!

确定后同步将在后台操作,完成时将刷新页面,请耐心等待。

一片 .sv 的 FPGA 知乎文章,让我找到了一个宝藏,就是今天的主角博主海军。SIGer 的访谈都会问受访人一个保留问题 “我的兴趣爱好” ,这个勤奋的码更人的博客直接给了我们答案。再考古他的公号,时点和 SIGer 非常接近,充满激情的文字,让我回想这两年 SIGer 的成长。而平行空间里的海军,则给同学们清晰地描绘了一位 FPGAer 的成长路线,带我们再问问他最初的选择,就可以封稿啦。最近《三体》热播,红岸基地的巨大功率的巡天天线,犹在耳边轰轰作响,本想再补个问题海军是否也喜欢,偏离主题太远,日后再请。

本期采取倒叙的方式,首先依照标题(这是挖掘出的宝藏,还有更多),文末再附上我们的考古路线,猫叔的笔记。

A Course in Radar Systems Engineering Prelude

Radar: Introduction to Radar Systems — Online Course

This set of 10 lectures, about 11+ hours in duration, was excerpted from a three-day course developed at MIT Lincoln Laboratory to provide an understanding of radar systems concepts and technologies to military officers and DoD civilians involved in radar systems development, acquisition, and related fields. That three-day program consisted of a mixture of lectures, demonstrations, laboratory sessions, and tours.

Overview

This course is presented by Robert M. O'Donnell, a former researcher at MIT Lincoln Laboratory, and is designed to instill a basic working knowledge of radar systems.

Description of Lectures

The set of 10 lectures starts with an introductory description of basic radar concepts and terms. The radar equation needed for the basic understanding of radar is then developed, along with several examples of its use in radar system design. Radar propagation issues such as attenuation, multipath effects, and ducting are described. The concept of radar cross-section, waveform design, antennas, transmitter and receiver characteristics, and the detection of radar signals in the presence of noise are presented. Some radars are required to detect small targets in the presence of much larger radar echoes from sea or land clutter in the radar's coverage. The characteristics of this clutter are discussed with moving target indicator (MTI) and Pulse Doppler techniques for mitigating the negative effects of clutter. The course continues with lectures covering target tracking and target parameter estimation. The last lecture discusses radar transmitters and receivers.

LIST OF LECTURES

Click on titles below to the view the lectures and/or download the pdf files of the viewgraphs for each lecture.

Lecture 1 – Introduction

View/Download Lecture 1 Viewgraphs (pdf)

Lecture 2 – Radar Equation

View/Download Lecture 2 Viewgraphs (pdf)

Lecture 3 – Propagation Effects

View/Download Lecture 3 Viewgraphs (pdf)

Lecture 4 – Target Radar Cross Section

View/Download Lecture 4 Viewgraphs (pdf)

Lecture 5 – Detection of Signals in Noise and Pulse Compression

View/Download Lecture 5 Viewgraphs (pdf)

Lecture 6 – Radar Antennas

View/Download Lecture 6 Viewgraphs (pdf)

Lecture 7 – Radar Clutter and Chaff

View/Download Lecture 7 Viewgraphs (pdf)

Lecture 8 – Signal Processing - MTI and Pulse Doppler Techniques

View/Download Lecture 8 Viewgraphs (pdf)

Lecture 9 – Tracking and Parameter Estimation

View/Download Lecture 9 Viewgraphs (pdf)

Lecture 10 – Transmitters and Receivers

View/Download Lecture 10 Viewgraphs (pdf)

讲师介绍:西安电子科技大学信号与信息处理专业硕士,从事算法工程师工作。

随着技术的进步,FPGA的应用场景也越来越广,从以前的控制、通信等领域发展到了并行加速计算 、人工智能算法加速等领域,但无论应用千变万化,时序约束都是Fpga中最重要的环节之一,也是很多FPGA工程师的盲点。

本教程详细讲解了FPGA的各种时序约束理论,并以一个实际的Vivado工程为例,一步一步进行时序约束,最终达到时序收敛。

前言:

时序约束是FPGA设计中最基本也是最重要的步骤之一,当然,也是难点之一。相信很多朋友都在网上看了不少讲时序约束的文章,对建立/保持时间一顿分析,自己好不容易理解了,发现并不知道这东西在实际中怎么应用。而且网上的时序约束文章虽然不少,但没有一个系统的教程,大部分都是只言片语,因此就萌生了做一个详细的关于时序约束教程的想法。本教程综合理解了网上和书上关于时序约束的资料,在后面也有一章节是专门针对实际工程进行的时序约束,对于刚刚接触FPGA的同学来讲,相信会有不小的帮助,对于FPGA的老手来说,也希望起到温故而知新的效果。好,废话不多说,开始正文。

本教程参考内容:

个人网站: http://www.technomania.cn/

微信公众号: Quant_Times & Reading_Times

读万卷书--时序约束理论篇 周期约束理论 首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多…

赞同 33

4 条评论

时序路径 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。 对于所有的时序路径,我们都要明确其起点和终点,这4类时…

赞同 42

5 条评论

I/O约束 I/O约束是必须要用的约束,又包括管脚约束和延迟约束。 管脚约束 管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值…

赞同 51

14 条评论

时钟周期约束 时钟周期约束,lo顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。 下面我们讲一些Vivado中时钟约束指令。 1.

赞同 41

7 条评论

两种时序例外 多周期路径 上面我们讲的是时钟周期约束,默认按照单周期关系来分析数据路径,即数据的发起沿和捕获沿是最邻近的一对时钟沿。如下图所示。 默认情况下,保持时间的检查是以建立时间的检查为前提,…

赞同 20

5 条评论

在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。 虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x÷都是按照…

赞同 9

1 条评论

行万里路--时序约束实战篇 我们以Vivado自带的 wave_gen 工程为例,该工程的各个模块功能较为明确,如下图所示。为了引入异步时钟域,我们在此程序上由增加了另一个时钟-…

赞同 17

添加评论

- 约束主时钟 在这一节开讲之前,我们先把 wave_gen 工程的 wave_gen_timing.xdc 中的内容都删掉,即先看下在没有任何时序约束的情况下会综合出什么结果? 对…

赞同 11

2 条评论

约束衍生时钟 系统中有4个衍生时钟,但其中有两个是MMCM输出的,不需要我们手动约束,因此我们只需要对 clk_samp 和 spi_clk 进行约束即可。约束如下: create_g…

赞同 12

2 条评论

- 延迟约束 对于延迟约束,相信很多同学是不怎么用的,主要可能就是不熟悉这个约束,也有的是嫌麻烦,因为有时还要计算PCB上的走线延迟导致的时间差。而且不加延迟约束,Viva…

赞同 15

5 条评论

伪路径约束 在不加伪路径的时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error。 我们可以直接在上面右键,然后设置两个时钟的伪路径。 这样会…

赞同 11

1 条评论

注:视频中5分37秒之后的内容有错误,在下面的文字部分已经删除,但视频不太好修改。请大家一定要注意,在这里向大家道歉。 多周期路径约束 多周期路径,我们一般按照以下4个步骤来约…

赞同 27

1 条评论

时序约束辅助工具 上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Cons…

赞同 30

5 条评论

Vivado时序约束中Tcl命令的对象及属性 在前面的章节中,我们用了很多Tcl的指令,但有些指令并没有把所有的参数多列出来解释,这一节,我们就把约束中的Tcl指令详细讲一下。 我们前面讲到过 get_…

赞同 24

4 条评论

你将获得

教学服务

讲师介绍:张海军

西安电子科技大学信号处理硕士研究生,曾任职中国科学院微小卫星创新研究院任职卫星通信算法工程师

课程详情

学习问题

这些知识点,都是初级的FPGA工程师转向高级FPGA工程师的必学技能!

课程亮点

内容概述与软件安装(3节)

| # | title | 试学 | len |

|---|---|---|---|

| 1. | 内容概述 | 试学 | 8分钟 |

| 2. | SystemGenerator的安装 | 试学 | 3分钟 |

| 3. | Matlab与Vivado的版本对应 | 试学 | 2分钟 |

微信公众号:Quant_Times

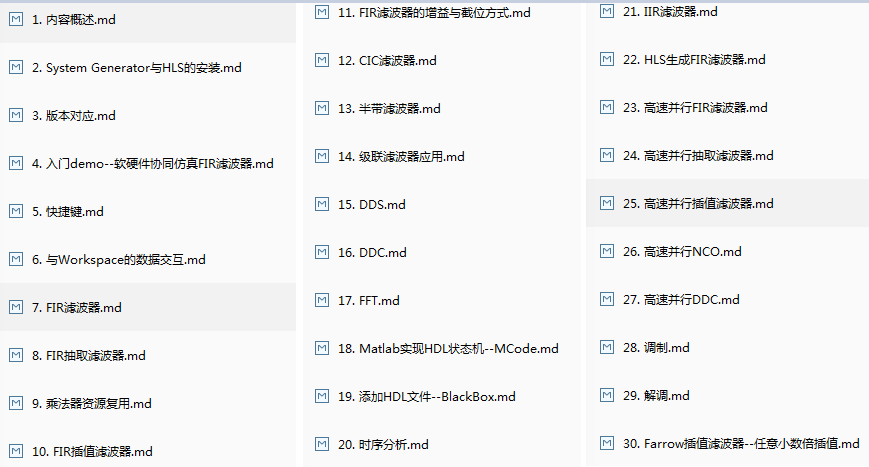

数字信号处理和FPGA有着密不可分的联系,现在市面上也有很多的FPGA做数字信号处理的教程,那为什么还要再出本教程呢?

目前市面上绝大多数的教程都是讲 ViVADO中的数字信号处理相关的 IP 的应用,而我们本次教程使用的工具是 System Generator 和 HLS,其中 System Generator 中的 IP 跟 Vivado 中的IP 用法很像,但用 SYSGEN 来完成算法的仿真比 Vivado要更快,更灵活;

市面上的教程大都是比较基础的,我们本次的教程则相对比较深入,比如滤波器系数的在线 reload、滤波器资源复用、多速率滤波器级联、高速并行滤波器、小数倍插值 Farrow 滤波器、IIR 滤波器、调制和时序分析等。这些都是初级 FPGA 工程师转向 高级工程师的必学技能。

视频+讲义的方式,更加容易学习。

Why System Generator and HLS

System Generator数字信号处理(一)(10节)

| # | title | 试学 | len |

|---|---|---|---|

| 1. | 入门demo--软硬件协同仿真FIR滤波器 | 试学(5分钟) | 20分钟 |

| 2. | SystemGenerator快捷键 | 9分钟 | |

| 3. | 与Workspace的数据交互 | 13分钟 | |

| 4. | SystemGenerator中FIR的详细使用方法 | 32分钟 | |

| 5. | FIR抽取滤波器 | 7分钟 | |

| 6. | 乘法器资源复用 | 6分钟 | |

| 7. | FIR插值滤波器 | 15分钟 | |

| 8. | FIR滤波器增益与截位方式 | 11分钟 | |

| 9. | CIC滤波器 | 12分钟 | |

| 10. | 半带滤波器 | 3分钟 |

System Generator数字信号处理(二)(8节)

| # | title | 试学 | len |

|---|---|---|---|

| 1. | 级联滤波器的应用 | 15分钟 | |

| 2. | DDS在SystemGenerator中的使用 | 10分钟 | |

| 3. | 数字下变频 | 10分钟 | |

| 4. | (快速傅里叶变换)FFT | 12分钟 | |

| 5. | Matlab代码实现HLS状态机--MCode | 5分钟 | |

| 6. | 在SystemGenerator中添加HDL文件--BlackBox | 7分钟 | |

| 7. | SystemGenerator中的时序分析 | 4分钟 | |

| 8. | IIR滤波器 | 14分钟 |

Vivado HLS数字信号处理(9节)

| # | title | 试学 | len |

|---|---|---|---|

| 1. | HLS手写FIR滤波器 | 40分钟 | |

| 2. | 高速并行FIR滤波器 | 12分钟 | |

| 3. | 高速并行FIR抽取滤波器 | 7分钟 | |

| 4. | 高速并行FIR插值滤波器 | 9分钟 | |

| 5. | 高速并行DDS | 7分钟 | |

| 6. | 高速并行DDC | 5分钟 | |

| 7. | 调制 | 16分钟 | |

| 8. | 解调(载波同步) | 试学(5分钟) | 27分钟 |

| 9. | 小数倍插值滤波器(Farrow滤波器) | 试学(5分钟) | 48分钟 |

各位同学大家好,欢迎观看本教程,我们本期的教程,来讲一下如何在FPT里面来完成初次镜像处理,其实这方面的资料在网上有不少,那为什么还要再出本教程?当然是我们更好一些,而且我们跟他们不一样,第一是因为现在市面上绝大多数的教程,他在讲镜像处理的时候,都是先讲一下镜像处理的某个算法,然后再讲vivado中跟这个算法相关的IP的应用,而我们本次教程主要是以system generator和vivado h rs这两个工具。来讲一下在这两个工具中,如何进行数字信号处理算法的设计与仿真。第二,就是市面上的大多数教程都是比较基础的,比如说他们在讲讲滤波器的时候,他们一般都只会讲滤波器系数,生成系数导入,以及这个滤波器IP的设置,但是,我们这个教程都讲的比较深入,比如说会讲一些,滤波器系数的,带线流漏的,有哪几种方式,我们可以在线重新配置它的系数。

然后滤波器资源的使用,根据滤波器资源的计算,多速率滤波器接连,这个就是讲KRC,半带跟FR滤波器,他们在多级的抽取和插值的时候,应该怎么去搭配,比如说第一级应该仿什么,第二级应该仿什么滤波器,哪一级滤波器的这个性能需要好一些,哪一级滤波器的性能不需要很好,高速并行滤波器,这个是因为我们现在adc的采样率越来越高,比如说像我们现在正在做的一个ad,它采样率有十个G,那像这么高的采样率,在维拉多中是没有一个线程的IP来供我们。可以完成信号处理算法的需要,我们自己去设计小数被插值fire滤波器,这个滤波器,在解调的未同步中是必用的,那有时候在调试中也会用到,比如说我们调制输出的速率的采样率是100兆,而而这个符号速率是1.01兆,那怎么从1.01兆,插值插到100兆这就是涉及小数被插值需要使用的fire滤波器,Ii滤波器,这个,可能可能网上资料会少一些。

就是说我们平时用的少一些,但这个呢在解调中是必备的,就是解调的辅相环中,他用的滤波器就是I ir滤波器,还有调制解调这些分析的,那这一些,都是初级的F飞机工程师转向高级工程师的必备技能。第三个就是我们是采用视频加讲义的方式,说起来,更加容易,而且更加直观。同时也欢迎大家关注我的微信公众号,观看我们会发布一些最新的资讯,也会整理一些技术文章,都是干货,欢迎大家关注。

下面来说一下我们为什么要选择facetime geniator和vivado h rs这两个工具。首先,Face镇,它是使用sing ulink在FPG中进行算法设计的一种解决方案。3X中有很多模块儿,它都集成到了sing u link中,所以说我,所以说,我们就可以直接通过拖拽的方式来设计算法,这样操作起来比较简单,而且,由于我们使用的都是,304提供的模块儿,所以face阵在生成HDR文件或者说网表的时候,它的结构都很清晰,而且我个人认为face阵是我们用ipg来做常规的数字信号处理。最好用的工具没有之一,那什么是常规的数字线上处理?就是我们在线上处理中最常用到的,比如说数字大变频f ir滤波器,CIC滤波器,半价滤波器,Ir滤波器,FFT跟DDS,以及由这一些延伸出来的,比如说各种级联的插曲,插值抽取,滤波器调制,就是说,凡是这些可以用就是现成的IP来完成的功能。

那我那我们使用非正去设计是最简单的,而且非正的设计理念,也是采用流水线结构,所以说我们FG工程师在学习起来是相对比较简单的,而且理解起来也相对更加容易。然后V89HRS是Phoenix推出的专门用来做算法设计的工具,那它是采用分加加来设计算法,分加加,它的设计理念跟我们在BG是有点区别的,所以说它的学习难度可能要大一些,而且,这个工具它主要是用来设计一些复杂算法。因为在常规的现象、数据、算法中,它它并没有非负震那么简单明了,但是,一对付它的算法,使用非负震打起来就比较麻烦,而且它的可一致性也不太好,那相当于八度的使用越来越简单,而且Felix也比较,而且也越来越推荐,使用全BD文件的形式去设计FPG程序,也就是说,我们也可以通过简单的拖拽IP跟连线的方式就可以完成一个程序的设计。所以说有同学就会有疑问,那我使用BD文件。

来设计线上处理的方法跟我使用非正确设计有什么区别?那最本质的区别就是我们产生仿真激励跟查看波形,因为我们线下处理算法都是需要需要先仿真的,就是要先仿真它的,它它输出结果是不是对的。如果我们使用Facebook的话,我们可以直接使用matlab去生成各种激励,跟查看波形,那这就很很方便,而且很强大,比如说我们要生成点评的调频的,包括调试信号,通过matlab程序,只需要几行代码就正常了,这远比大理八度中去写TP文件要。要方便很多,而且我们使用matlab去查看它的波形也很快,也要比伟大斗争去去去看波形要更更直观一些,也就是说,我们使用非线去开发跟使用BD文件开发的开发速度是完全不一样的。当然也有,也有也有一些更高端的玩家,他们会使用python中的my Excel这个库来设计FPG的算法,那这个库确实是一个很好的库,可以用python来写出很多复杂,而且易用的FPG的算法模块。

如果以后有机会的话,我也会出一个出一个这方面的教程,然后我们本次教程,大概分为两部分,第一部分是讲facetime geniator,主要是第第第三章到第21章,然后第二部分,是讲VR的HS是22章到第30章,然后为了跟我们这个课件相匹配。所以说,所以说我们的视频,就是每一个视频会讲其中的一章,那这样,就会导致我们每个视频长度不一样,短的,可能是两分钟三分钟四分钟长的,可能是30分钟40分钟,那好我们这节课就先到这里,我们下节课来讲一下软件的安装,好谢谢大家。

原创 张大侠 傅里叶的猫 2022-12-31 20:55 发表于上海

[图片上传中…(image-n9Byk6WHPtzGNHHt7NI0)]

2022年又要结束了,回顾今年的种种,依然历历在目,最大的感慨就是“人到中年,身不由己”。

突如其来的家庭变故,让我感受到了前所未有的压力,不论是精神压力还是经济压力,都是以往所没有的。

但生活还是要继续,我们还是要往前看,相信一切都是最好的选择。

今年的公众号推文比往年要少了很多,一方面是由于花了很多精力在家人身上,另一方面也是工作太忙,加班比较多,有段时间一度经常加班到晚上10点多。

今年的推文主要以FPGA为主,其他方面的文章都少了,我们以后也会更加集中精力在FPGA上,当然肯定会涉猎其他方面,在有精力的前提下,还是会多写一些。

今年的广告发的也比较少,一方面是因为感觉今年的金主爸爸也没啥钱了,另一个方面跟自己的活跃度低了也有关系。

在新的一年,我们希望可以写一些系列性的文章,下面是我的几个初步想法,希望2023年可以写出来:

今年我们也希望可以做一些有意思的作品出来,而不只是写博客。一方面看的也好玩,也可以为以后自己想做的东西做些准备。

新年的钟声即将敲响,让我们怀着对未来的美好向往,共同迎接2023年的第一缕阳光。

祝愿祖国繁荣昌盛、国泰民安!祝愿世界和平美好、幸福安宁!祝愿大家新年快乐、皆得所愿!

原创 张大侠 傅里叶的猫 2021-12-31 23:26

2021年马上就结束了,再过不到一个小时,就是新的的一年。趁着还没到零点,我们赶紧来做一次年终总结,汇总一下今年都做了哪些事情。

公众号的主要任务还是写文章,今年我们一共进行了90次的推送,绝大部分文章都是原创的技术性文章,也有些是从是德科技转载而来。主要包括下面几类:

在年初时也写过几篇格局类的文章,很多都是本人平时看书时的一些感想,后来在家看书的时间少了。这类文章写的就少了,争取明年还是在这方面在多写一些。

今年年中时,博主换了一份工作,从公众号发文的内容也可以看出来,从那之后发的文章基本都是跟FPGA相关的了,其他类型的相对少了一些。

今年换工作真是花了自己不少的精力,一直没有定下来以后要做的方向,面了很多公司,准备面试也是花费了很多时间,有时间就会刷题、看可能的面试内容。但准备的方向太多,总体花的时间就非常的多了。不过好在最终确定下来继续做FPGA方向,这个自己做了7、8年的东西。

我们对自己的定位就是用Python的FPGAer,我们也希望能用一些更上层的语言来开发FPGA,节省开发时间。所以后面我们还是会出一些其他方面的内容,更会介绍一些新的“开发姿势”。

在2020年元旦,我们十多位IC行业的公众号号主,共同建立了一个"IC技术圈"。如今群里已经有99位博主,汇集了众多来自于知名企业和高校的资深FPGA/IC从业者,每个月都会发一次IC技术圈期刊,或分享经验、或传授技巧,或聊求职就业,或谈人生规划,欢迎大家持续关注了。

今年我们的参与度确实较去年下降了很多,明年争取每个月都参与,让IC技术圈发展越来越好。

今年公众号还有一件大事就是改名,现在公众号的名字是“傅里叶的猫”,由于博主本身是信号处理方向出身,之前也一直在做信号处理的工作,所以觉得傅里叶的猫这个名字既形象,又可以筛选目标群体。

最后,引用的新年贺词:

新年的钟声即将敲响。我们的三位航天员正在浩瀚太空“出差”,海外同胞仍在辛勤耕耘,使领馆、中资企业等海外派驻人员和广大留学生仍在勇毅坚守,无数追梦人还在奋斗奉献。

让我们一起向未来!祝福国泰民安!

原创 张大侠 傅里叶的猫 2021-01-01 09:09

元旦快乐

新年第一天,首先要对大家说一声Happy New Year!!!

凡事预则立,年度计划是我们新的一年里的头等大事。今年公众号我们将着重考虑下面几点。

公众号是由我和师弟大亮一起运营,去年的SLAM标定系列就是大亮写的。今年我们还会将去年的几个系列持续进行下去,并将在此基础上增加与之前内容相关的系列。由于正在准备《Julia高性能计算》一书,因此Julia的内容又被重新提上了文章发表的日程。

我们计划的文章系列如下:

系列性的文章,肯定要求我们更加专业。作为从业人员,我们写的内容基本都是平时所学所用的整理与汇集。今年我们还会继续写出更加专业性和更加实用性的文章,让大家不会白花时间。

油管上有很多好的视频教程,虽然都是英文的,但对于专业性的从者们来说,即使不能全部听懂,也基本能够理解视频所要表达的意思。因此我们今年还会将油管上好的学习资料搬运过来,供大家参考学习。

国内的很多高校BBS上也有大量的好资料,比如六维空间、北邮人,我们西电的睿思等等,只是毕业后大家基本都不能上教育网,也就不能去这些网站上下资料。好在本人目前还可以上其中一个,在发现好的资料时,也会将资料分享出来,供大家免费下载。

关注我们,资料不断。

最近又重新看了一遍吴军老师的《格局》,感觉每次看都有新的收获。作为码农、作为工程师、作为打工人,不仅要低头拉车,还要抬头看路。我们不应指只把自己的眼光停留在代码的调试上,应该把自己的格局提高一个层级。

这个时代发展太快,我们要时刻关注最新的科研技术,了解时代发展的轨迹。因此今年我们会在公众号中增加一些科技成果资讯、大公司的发展中不太为人知的关键事件和个人对很多事的观点。

小目标已定,若年底总结时未能实现,欢迎大家前来挖坟。

最后,引用的新年贺词:

此时此刻,华灯初上,万家团圆。新年将至,惟愿山河锦绣、国泰民安!惟愿和顺致祥、幸福美满!

原创 张大侠 傅里叶的猫 2020-12-31 08:08

2020庚子年已过,2021辛丑年就要到来。这一年我们的都做了哪些事情?又得到了什么样的结果?

2020已经快要结束,明天就是新的一年。按照传统,我们还是来一次年终的总结,总结今年我们都做过哪些事情。对于2021年的展望,我们放到明天的文章中。

2020年年初,正好赶上了新冠疫情,整个国家都在坐月子。但我们也并没有闲着,在2020年元旦,我们十多位IC行业的公众号号主,共同建立了一个"IC技术圈"。

经过几个月的发展,现在已经有60多位成员。汇集了众多来自于知名企业和高校的资深FPGA/IC从业者,其中不乏业界的几位大佬,如 路科验证的路桑 , 老石谈芯的老石 ,还有将我们组织在一起的 ExASIC 陈锋 。

在每个月中旬发一次IC技术圈期刊,或分享经验、或传授技巧,或聊求职就业,或谈人生规划,欢迎大家持续关注了。

公众号的主要任务还是写文章,今年我们一共进行了94次的推送,当然其中也包含了部分商业推广和重复发送的内容,但绝大部分文章依然是原创的技术性文章。而且种类也比较丰富,包含FPGA/GPU/Python/Matlab/信号处理/C++/Julia/计算机视觉。

其中阅读量最多的几篇文章是:

今年我们还针对性的出了很多系列教程,这些系列教程我们后面还会继续出下去。文章如果太分散,不利于大家的理解与掌握,只有系列化、规范化才是做好一件事的必备条件。

今年的系列教程包括:

在今年是双十一时,我们也推出了System Generator & HLS数字信号处理的视频教程,这也是本人推出的第一个收费的视频教程。

在网易云课堂、腾讯课堂和移知官网都可以搜到,到现在不到两个月的时间,已经有150多个同学进行了学习。

本课程详细讲解了如何使用System Generator(也就是Simulink)和C++来进行常规的数字信号处理和高速并行的数字信号处理,最后讲了如何进行调制解调、任意小数倍插值滤波器。对于FPGA/数字信号处理的入门同学和老司机们都会有帮助。

教程目录如下:

这里我们再提一下之前出过的两个系列教程,都是免费的视频教程,而且在网上都获得了广泛的好评。

这两个视频教程的讲义都在公众号中回复“Julia”和“FPGA”即可获取。

在B站上有两个Julia的视频教程,后面一个才是我发的,一定要注意。因为我之前没怎么上过B站,注册会员考试失败图片,也就一直没有往B站上发。这期间有个up主从网易云课堂上下载的课程并发到了B站,由于他注明了出处,因此我并没有去追究。

今年下半年,有幸接到清华大学出版社的邀请,出版《Julia高性能计算》一书,该书将分为两部,第一部是讲Julia的初级教程,主要讲Julia基础语法、元编程和并行计算。第二部讲Julia的高级应用,主要讲Julia的高性能优化,Julia在机器学习/深度学习中的应用。在复旦大学读博的师妹将跟我一起完成这两本书,第一本将在明年的上半年与大家见面,欢迎大家关注。

细心的朋友可能发现,作者名字改了,之前作者名是猫叔,现在是张大侠,正所谓侠之大者,为国为民。我们现在正在做的事,已经对很多朋友起到了些许的帮助。希望所学所用能够为社会贡献更大的力量!

原创 Rex 杉杉成长日记 2019-09-01 11:10

这一年确实太忙了,早就应该出来的读书内容硬是拖了这么久。从今天,就开始我们的财经读书之旅。

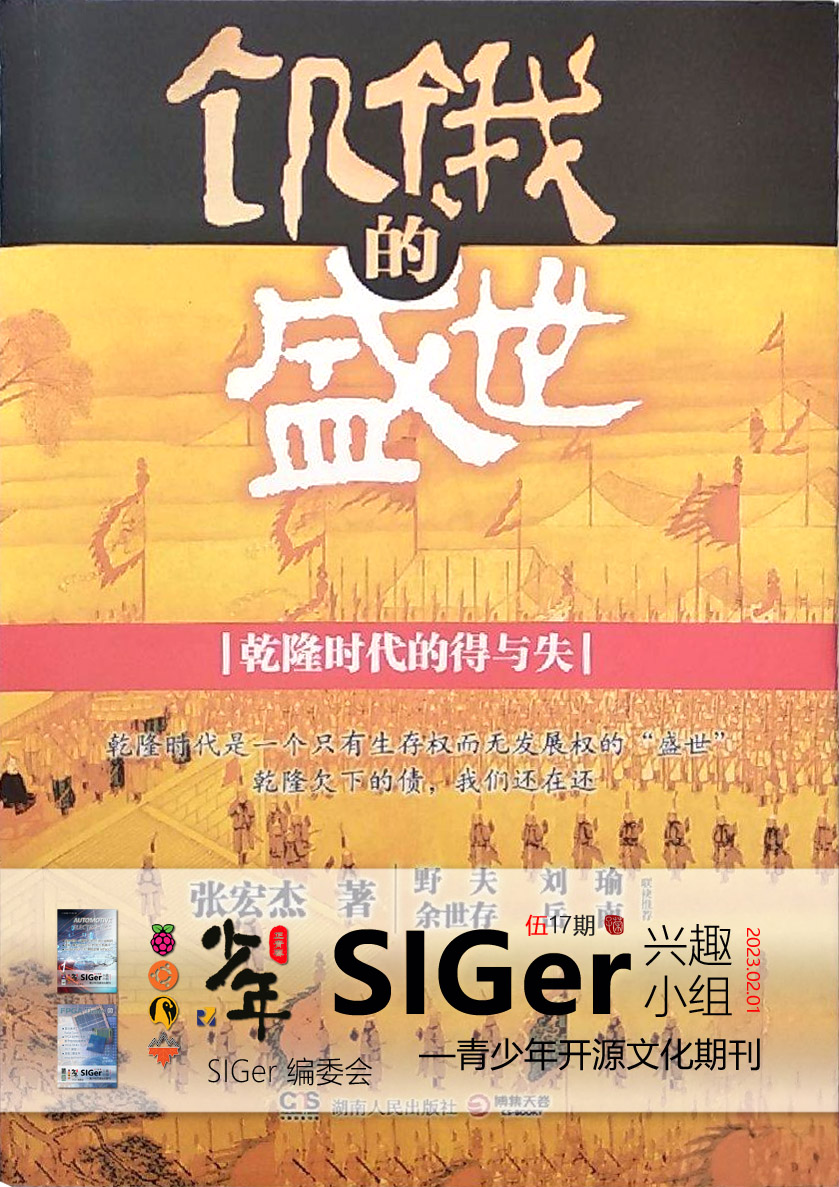

在2018年,《延禧攻略》和《如懿传》大火,演的就是乾隆时期后宫的事情,我们都听过康乾盛世,而且乾隆时期的盛世是传统中国的巅峰,GDP占全球三分之一,国库充盈,四海臣服,但光鲜的外表却掩盖不了内在的腐烂。那到底乾隆时期真实的情况是怎么样的呢?是不是像如懿传中乾隆跟第二任皇后乌拉那拉氏非常恩爱呢?我们将在这本张宏杰先生的《饥饿的盛世》一书中得到答案。

乾隆12岁那年,在他父亲雍亲王的精心策划下才第一次见到康熙, 对于现在的我们可能非常不能理解,为什么孙子到了12岁才第一次见到爷爷,要知道康熙有97个孙子,能见到政务缠身的老皇帝的不到一半。

乾隆的母亲是钮祜禄氏,并非名门望族,刚开始进入雍亲王府时只不过是一名普通的丫头,干些端茶倒水之类的杂活,身份低微,所以说乾隆的出身其实不算好,

而当时康熙最喜欢的孙子是太子的儿子弘晳,也希望这个孙子将来能继承皇位,所以虽然知道太子不堪重用,但却在废太子的问题上迟迟下不了决心。

原创 Rex 杉杉成长日记 2019-09-02 12:26

各位朋友大家好,昨天我们读到了张廷玉找乾隆辞职,但乾隆不肯。

皇帝觉得虽然你有点老糊涂,但这么多年的经验还是很丰富的,作为朝中顾问还是可以再用几年的。而且张廷玉配享太庙这项殊荣,理应为国家贡献出全部力量。

但张廷玉却说你看看你人明太祖朱元璋,人家就允许配享荣誉的大臣退休回家。皇帝一听能不生气么,就怼回去:朱元璋那是把大臣罢斥回乡,并非大臣主动请求;你怎么不学点好,看看人家诸葛亮,鞠躬尽瘁,死而后已。

第二天,皇帝就把他们的对话昭告天下,让天下的人都不占在张廷玉一边。

又过了一段时间,年近八旬的张廷玉又向乾隆提出退休,乾隆也看到他已经老态龙钟,说话也经常颠三倒四,就动了恻隐之心。说:我非常舍不得你,但你现在年时已高,去或留的你自己决定吧。他心想张廷玉应该会表达出对自己的依依不舍,但苦于老病,只能退休。这样他也就放放他回去了,

但张廷玉也可能是老糊涂了,没能理解皇帝的意思,当即谢恩,说明年春天就走。即便这样,皇帝也表现出难得的宽容和善意。他想与张廷玉有始有终。如果张廷玉就这么走了,事情也算完了,可惜,人生往往就是那么难以捉摸。

他怕这么一走,配享太庙的资格就没了,在家犹豫多日后,豁出自己那张老脸,去见皇帝想跟皇帝要一张保证。

乾隆也很郁闷啊,这不没事找事么,我从来没数过收回你这配享太庙的权利啊,但送佛送到西,念在三朝元老的面子上,给他写了首诗,大意是也不知道当时父皇是怎么想的,能让你配享太庙,现在我也不说什么了。

张廷玉拿到这诗,如获至宝啊,按理说第二天他应去面圣谢恩,但毕竟年纪大了,前一天的面圣又消耗了太多精力,只能让儿子代替自己去谢恩,

皇帝又是大怒,并下旨到了军机处,令张廷玉“明白回奏”是怎么回事,但正好军机处的大臣是张廷玉的门生,把这事偷偷告诉了张廷玉,此时张廷玉又办了一件糊涂事:跑到皇帝面前谢罪。这不明摆着说有人向他传递龙颜大怒的消息么。而乾隆一向是最提防朋党的,这次他真的生气了,把前前后后的糊涂账一起算上,大骂张廷玉:配享太庙的都是佐命元勋,你有什么资格配享?不过事实也确实如此,鄂尔泰尚有平定苗疆之功,张廷玉却只是当了一辈子的好秘书,并没有什么拿得出手的功绩。

虽然这么说,但毕竟太庙的事是父皇说的,他也就没有收回,只是把张廷玉的伯爵削去,张廷玉觉得自己也没脸再待下去了,就想等来年春天就起程回乡。不料,他选择的回乡日期刚好是皇长子去世的日子,他是皇长子的师傅,必须参加丧礼,但丧礼刚一结束,他马上就跟皇帝说要走,皇帝本来就很重视这个长子,而且当时十分悲伤,本来皇帝心情不好就要拿大臣出气,结果被张廷玉给碰上了,乾隆觉得张廷玉太缺少人情味,并且毫无中心,不够配享太庙的资格。并拿出历代配享之臣的名单,甩在张廷玉脸上,让他看看自己是不是不配?是不是应该放弃这个资格?

这是群臣也附和皇帝,说张廷玉不配资格。张廷玉也知道事情已经到了无法挽回的地步,就说自己确实不配,灰溜溜的回家了。

回到老家后的张廷玉闷闷不乐,不久后,他的亲家因为匿丧赶考被举报,此时皇帝又想起了张廷玉,觉得他怎么会跟这样一个品行卑污之人结成亲家,这真是欲加之罪何患无辞,于是皇帝又决定收回以往三代皇帝对张廷玉的一切赏赐,以示惩罚。就命人去家中收缴,但说是收缴,实为抄家,乾隆想看看张廷玉家里有没有对自己怨念的词。但老狐狸还是老狐狸,他的书中只详细记载了三朝皇帝对他的“恩遇”“赏赐”,虽然细到哪一天皇帝说过哪句赞赏他的话,但关于政治和抱怨的话,一句也没有。

乾隆碰了一鼻子灰,也只能说那个官员理解错自己的意思了,但谁都能看得出来,这就是乾隆的旨意。

经历了这一次的事件,张党完全被击垮。张廷玉名誉丧尽,门生故吏各寻出路,如树倒猢狲散,乾隆打击朋党,终于以全胜结局。

张廷玉就这样在家中苟活了5年,郁郁而终。消息传来,乾隆也感到一丝悲痛。毕竟他们君臣相处了十四年,回想起张廷玉一生的所作所为,他感觉自己对张廷玉确实苛刻了点。于是他又做出一副皇帝做出眷念老臣之姿态,宣布宽恕张廷玉的一切过失,仍然命他配享太庙。并写了一首诗来怀念张廷玉,意思大致是:虽然你有错,我仍没有严厉惩罚,仍许你配享太庙,我对你如此宽容,希望你在地下能感激。

这里要再多说一点,乾隆时期平定新疆占戈争是进入全盛的标志,基本上对整个中国都实现了统一,这也是中国历史上最后一个盛世。

乾隆对大臣是这样的态度,那他对普通的民众呢?乾隆从小接受帝王教育,对农民生计之艰也颇多了解。因此他对劳苦大众还是非常仁慈的。有次安徽太湖闹饥荒,灾民们吃一种黑米为生,乾隆得知后,亲口尝试,不禁潸然泪下。他还分给几位皇子,让他们了解民间疾苦

还有一次,山东德州发生水灾,但当地督粮的官员去省城办事,他母亲就令人开仓赈济灾民,后来这事被举报到乾隆那里,理由是蔑视国家体制。但乾隆愤然回复到:有这样的母亲和好官,你们不但不举荐,还要弹劾。这位官员就是因为有了这样一位母亲很快就升到了督抚之位。

虽然乾隆年间的救灾也无法避免人治社会中常见的侵吞干没,层层盘剥,但是纵向比较中国历史,仍然可以肯定地说,乾隆是传统社会中采取救灾措施最为得力的统治者。

熟读历史的乾隆知道,饥饿的农民是国家最危险的敌人,而温饱了的农民则是皇权最坚定的支持者。所以乾隆鼓励农民开荒,还把免除了全国范围内拖欠多年的农业税,据统计,乾隆前前后后一共少收农民白银1.4亿两,粮食1200万石。据《清代国家与社会》一书提供的数字,乾隆一朝所减免的农业税总数为2.0275亿两白银,是中国历朝之冠。约合现在的人民币405亿,猛的一听感觉也不多呀,但如果换一种算法,乾隆减免的农业税占乾隆朝财政总收入的7.57%,而我国的个人所得税只占财政收入的6%,这相当于免除全国人民的个税,这可是一笔不小的数目。

都说乾隆时期是盛世还有个原因就是人口的激增,但这也不能都是乾隆的功劳,因为乾隆年间全世界的人口都在增长,这主要得益于红薯和玉米这两种18世纪的食物革命,这两种作物成活率高,一下解决了很多人吃饭的问题,在乾隆60年的统治生涯中,中国的人口增长了一倍,确切地说,增长了108%,比世界水平高出了65个百分点。18世纪初,中国人口占世界人口比重为23.4%,到这个世纪末则达到了34.06%。

乾隆朝农业发展的标志性成绩是全国粮食产量的增加,中国历代口粮总量发展呈总的上升趋势。其中秦汉为417亿斤,唐代为626亿斤,宋代为835亿斤,明代为1392亿斤。而到清乾隆晚期,一跃而达2088亿斤,并达到历史最高水平。正是农业的成绩,使乾隆朝的人口发生爆涨,支撑各项社会经济发展指标达到中国历史的极峰。

我们再来看看乾隆时期的占戈争,数代以来,准噶尔汗国一直是大清王国最大的威胁。他们长期生活在新疆青海一带,虽然在康熙年间,大清击败了噶尔丹,但事实上,准噶尔汗国仅仅遭遇了挫折,远远没有被打垮,他们又慢慢壮大起来,还经常时不时骚扰一下大清。

要不说乾隆福气好呢,到了乾隆年间,准噶尔部开始分裂,其中有一部分主动归顺了清朝。他也觉得此时正是准噶尔汗国最虚弱的时期,应当迅速出兵。

但他的这个决定却遭到文武百官的反对,因为乾隆在和平中接了班,大清已经很久没有打过仗,除了那场本没有必要的金川占戈争之外,大清不闻兵戈之声。而且中原王朝一直以来对于出兵打少数民族那叫一个头疼。那后来的事情又是怎样的呢?乾隆有没有出兵呢?我们明天继续讲。

使用SystemVerilog简化FPGA中的接口 【转载】

OrangeCrab Open-Source FPGA Development Board :Now at element14 ₹46.72

GaN Adoption Rises for FPGA Power Design - EE Times Europe

eetimes.eueetimes.eu|1334 × 794 jpeg|Image may be subject to copyright.

FPGA brings high speed SERDES to RF and communications applications

https://max.book118.com/html/2021/0531/8142107015003105.shtm

zz张大侠 B站:https://space.bilibili.com/336070807 【摘要】

FPGA Times 【目录】 51

猫叔个人网站:http://www.technomania.cn/

EEtimes : Can TI Obsolete FPGAs? 【转载】

FPGA times : https://www.eetimes.com/

iPhone 14 Pro's New Ambient Light Sensor – Inside the Package - EE ...

eetasia.com|2799 × 853 png|Image may be subject to copyright.

他的专栏

科学计算

41 篇内容1,728 赞同

微信公众号:傅里叶的猫

51 篇内容1,015 赞同

一种HDL新写法

2 篇内容2 赞同

信号与信息处理 硕士 公众号:傅里叶的猫

self-intro | 8621 | 2019-7-30

一个简单的自我介绍和个人主页的介绍

川普大选期间的乌龙事件 | 920 | 2020-11-22

费马猜想有哪些?为什么数学家们花了数百年时间去证明? | 7820 | 2020-4-23

作为一个业余数学家,费马提出了哪些猜想?为什么能让数学家证明数百年?

雷达系统工程 Radar Systems Engineering | 53571 | 2020-2-6

FPGA时序约束教程 | 2.8万 | 71 | 2019-10-22

讲师介绍:西安电子科技大学信号与信息处理专业硕士,从事算法工程师工作。 随着技术的进步,FPGA的应用场景也越来越广,从以前的控制、通信等领域发展到了并行加速计算 、人工智能算法加速等领域,但无论应用千变万化,时序约束都是Fpga中最重要的环节之一,也是很多FPGA工程师的盲点。 本教程详细讲解了FPGA的各种时序约束理论,并以一个实际的Vivado工程为例,一步一步进行时序约束,最终达到时序收敛。

Julia教程 从入门到进阶 | 1.7万 | 30 | 2019-7-31

Julia是一门“新兴起”的科学计算语言,在数据分析和科学计算领域优势非常明显。 讲师介绍:西安电子科技大学信号与信息处理专业硕士,从事算法工程师工作。 作为网上第一个免费的完整的Julia视频教程,本系列Jullia教程面向对数据处理和Julia感兴趣的同学,希望大家能把教程里面的代码都动手打一遍,能做到对Julia语法真正掌握,对Julia中的各种库真正的熟悉。有问题的同学可以在课堂下面留言,或者到微信公众号:Quant_Times中留言,我们一起讨论。

https://github.com/Rex1168/rex1168.github.io

https://github.com/Rex1168/Verilog-Template

https://gitee.com/RV4Kids/Verilog-Template

pic

FpgaTool

Description: This gui/script is used to generate verilog instance. There are two methods you can use.

Method1: Use the gui. Demo

Method2: Use script directly. Demo

https://github.com/Rex1168/youdao2github

README.md

This repository is used to change markdown's image link from youdaoyun to github.

Cause of this repository :

Md2All could not recognize md's image link from youdaoyun.

Using steps :

step1: Put youdaoyun markdown file to md folder.

step2: Change the file_name and img_name in downYoudaoImage.py, and run the file, then you will see the images downloaded from youdaoyun.

step3: Push the image files to github.

step4: Change the githubImgUrl in replaceYouDaoImageUrls.py to your actual url, and run the file.

step5: Done! Check the new.md.

downYoudaoImage.py

# -*- coding: utf-8 -*-

import re

img = r'!\[.+\]\(.+\)'

fileDir = './md/'

filename = 'text.md'

ImgUrls = []

imgDir = './img/'

img_name = 'timing_toturial'

def getUrls(filename):

with open(filename,'r',encoding='utf-8') as f:

text = f.read()

MdImgUrls = re.findall(img, text)

for itm in MdImgUrls:

pos = itm.find('(')

ImgUrls.append(itm[pos+1:-1])

# print(itm)

def urllib_download(urlLst, imgDir):

from urllib.request import urlretrieve

for idx,url in enumerate(urlLst):

urlretrieve(url, imgDir + img_name + str(idx) + '.png')

if __name__ == "__main__":

getUrls(fileDir + filename)

urllib_download(ImgUrls, imgDir)

repalceYoudaoImageUrls.py

# -*- coding: utf-8 -*-

import re

img = r'!\[.+\]\(.+\)'

fileDir = './md/'

filename = 'article.md'

# ImgNum = 60

githubImgUrl = 'https://raw.githubusercontent.com/Bounce00/pic/master/fpga/timing_toturial'

def replaceUrls(filename):

with open(filename,'r',encoding='utf-8') as f:

text = f.read()

MdImgUrls = re.findall(img, text)

for idx, itm in enumerate(MdImgUrls):

pos = itm.find('(')

youdaoUrl = itm[pos+1:-1]

githubUrl = githubImgUrl + str(idx) + '.png'

text = text.replace(youdaoUrl, githubUrl)

return text

def writeNewFile(fileDir, text):

with open(fileDir + 'new.md', 'w', encoding='utf-8') as f:

f.write(text)

if __name__ == "__main__":

text = replaceUrls(fileDir + filename)

writeNewFile(fileDir, text)

md/new.md (empty)

md/test.md

[TOC]

# 前言

时序约束是FPGA设计中最基本也是最重要的步骤之一,当然,也是难点之一。相信很多朋友都有过跟我一样的经历,看网上很多讲时序约束的文章,对建立/保持时间一顿分析,自己好不容易理解了,发现并不知道这东西在实际中怎么应用。而且网上的时序约束文章虽然不少,但没有一个系统的教程,大部分都是只言片语,因此就萌生了做一个详细的关于时序约束教程的想法。本教程综合整理了网上和书上关于时序约束的资料,在后面也有一章节是专门针对实际工程进行的时序约束,对于刚刚接触FPGA的同学来讲,相信会有不小的帮助,对于FPGA的老手来说,也希望能起到温故而知新的效果。好,废话不多说,开始正文。

本教程参考内容

- 《vivado从此开始》

- 《FPGA设计实战演练 高级技巧篇》

- 《ee5375_timing_fpga》

- Xilinx的各种UserGuide

- 网上各个论坛(csdn、知乎、简书)

# 读万卷书--时序约束理论篇

## 1. 周期约束理论

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

周期约束就是告诉软件我们的时钟周期是多少,让它PAR后要保证在这样的时钟周期内时序不违规。大多数的约束都是周期约束,因为时序约束约的最多是时钟。

在讲具体的时序约束前,我们先介绍两个概念,在下面的讲解中,会多次用到:

- 发起端/发起寄存器/发起时钟/发起沿:指的是产生数据的源端

- 接收端/接收寄存器/捕获时钟/捕获沿:指的是接收数据的目的端

### 建立/保持时间

讲时序约束,这两个概念要首先介绍,因为周期约束其实就是为了满足建立/保持时间。对于DFF的输入而言,

- 在clk上升沿到来之前,数据提前一个最小时间量“预先准备好”,这个最小时间量就是建立时间;

- 在clk上升沿来之后,数据必须保持一个最小时间量“不能变化”,这个最小时间量就是保持时间。

<center>

</center>

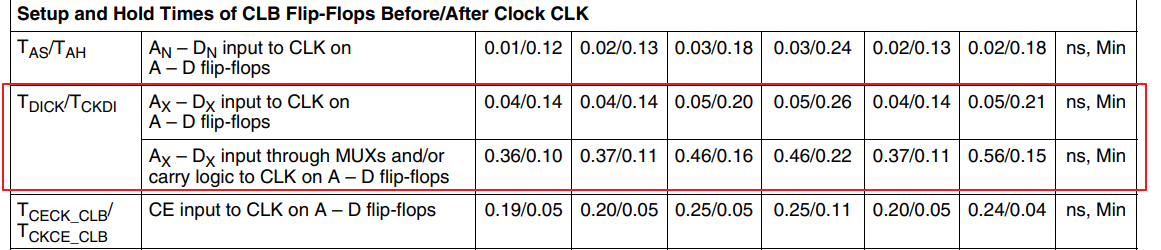

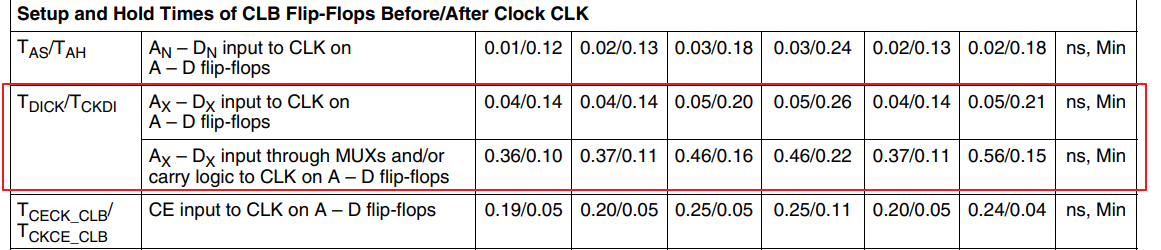

建立和保持时间是由器件特性决定了,当我们决定了使用哪个FPGA,就意味着建立和保持时间也就确定了。Xilinx FPGA的setup time基本都在0.04ns的量级,hold time基本在0.2ns的量级,不同器件会有所差异,具体可以查对应器件的DC and AC Switching Characteristics,下图列出K7系列的建立保持时间。

<center>

</center>

前言

时序约束是FPGA设计中最基本也是最重要的步骤之一,当然,也是难点之一。相信很多朋友都有过跟我一样的经历,看网上很多讲时序约束的文章,对建立/保持时间一顿分析,自己好不容易理解了,发现并不知道这东西在实际中怎么应用。而且网上的时序约束文章虽然不少,但没有一个系统的教程,大部分都是只言片语,因此就萌生了做一个详细的关于时序约束教程的想法。本教程综合整理了网上和书上关于时序约束的资料,在后面也有一章节是专门针对实际工程进行的时序约束,对于刚刚接触FPGA的同学来讲,相信会有不小的帮助,对于FPGA的老手来说,也希望能起到温故而知新的效果。好,废话不多说,开始正文。

本教程参考内容

读万卷书--时序约束理论篇

周期约束理论

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

周期约束就是告诉软件我们的时钟周期是多少,让它PAR后要保证在这样的时钟周期内时序不违规。大多数的约束都是周期约束,因为时序约束约的最多是时钟。

在讲具体的时序约束前,我们先介绍两个概念,在下面的讲解中,会多次用到:

建立/保持时间

讲时序约束,这两个概念要首先介绍,因为周期约束其实就是为了满足建立/保持时间。对于DFF的输入而言,

建立和保持时间是由器件特性决定了,当我们决定了使用哪个FPGA,就意味着建立和保持时间也就确定了。Xilinx FPGA的setup time基本都在0.04ns的量级,hold time基本在0.2ns的量级,不同器件会有所差异,具体可以查对应器件的DC and AC Switching Characteristics,下图列出K7系列的建立保持时间。

最近ChatGPT大火,成功破圈,到底是什么?怎么使用? 简单说,它是一个模型,一个语言模型! <b data-first-child="它是以对话方式与人进行交互的AI语言模型! 但它能做的事情太多了,可以用它来写一封请假邮件: 还有人用它来学英语、向它提各种问题,甚至可以用它来写程序,很多软件工程师都尝试过用它来写Python、Java等编程语言,这里我们就不再尝…

赞同 17

3 条评论

在平时工作中,经常会听到哪个FPGA或者某个芯片包含了几百万门,每次听到这种数字,很多FPGA工程师都会一愣一愣的,因为大家工作中,说的逻辑资源数量,一般是指CLB或者Slice的个数,没人会特指…

赞同 7

1 条评论

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。 elaborate可以翻译为“详尽解析”,就是将RTL源代码翻译转换成对应的电路。 有同学会问,这不是Synthesis做的工作…

赞同 14

2 条评论

vivado有project模式和non-project模式,project模式就是我们常用的方式,在vivado里面新建工程,通过GUI界面去操作;non-project模式就是纯粹通过tcl来指定…

赞同

添加评论

在ubuntu上安装vivado2021.1时,一直卡在最后一步:generating installed device list 安装其他版本也出现过该问题。 这是因为ubuntu中缺少库文件支持,安装下面几个库: sudo apt-get updatesudo apt-get upgradesudo apt-get…

赞同 4

3 条评论

上一篇我们讲过set_input_delay: 什么是output_delay? 顾名思义,output_delay就是指输出端口的数据相对于参数时钟边沿的延时。 对于系统同步,FPGA和下游器件是同一…

赞同 2

1 条评论

set_input_delay属于时序约束中的IO约束,我之前的时序约束教程中,有一篇关于set_input_delay的文章,但里面写的并不是很详细,今天我们就来详细分析一下,这个约束应该如何使…

赞同 7

3 条评论

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟: 但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。 首先,虚拟时钟用于什么地方? 虚拟时钟通常用…

赞同 9

添加评论

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Micro…

赞同 3

4 条评论

FPGA中BEL Site Tile FSR SLR分别指什么?

在Xilinx FPGA中,从底层到整个设备可以划分为6个层次: BEL Site Tile FSR SLR Device 下面我们从下到上依次来看一下各个定义。 BEL(Basic Element of Logic) BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BE…

赞同 13

2 条评论

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错,比如: 报的错误是dac_spi_i0/bit_cnt[4]_i_4的这个LUT有个输入悬空了,这个工程的逻辑比较简单,例化的嵌套也比较少,因此在schematic一层层找也很容易可以找到,但如果工程比较复杂,在…

赞同 3

添加评论

Xilinx FPGA中HP HR HD bank分别是什么用途

在开发FPGA绑定管脚时,经常会看到HP Bank、HR Bank和HD Bank,它们分别是什么意思?分别可以适用于哪些应用个? 首先我们要明确一点,这几个概念都是在7系列之后才有的,其中7系列的FPGA中有HP Bank和HR Bank,UltraScale FPGA有HP Bank、HR Ba…

赞同 6

添加评论

在FPGA的时序约束中,主时钟约束是第一步就要做的,主时钟通常有两种情形:一种是时钟由外部时钟源提供,通过时钟引脚进入FPGA,该时钟引脚绑定的时钟为主时钟:另一种是高速收发器(GT)的时钟RXO…

赞同 9

3 条评论

在FPGA的开发中,对于两个异步时钟,如果我们可以在RTL的设计中保证这两个时钟域之间的处理都是正确的,那就可以让工具不分析这两个时钟域之间的交互。如果不设置的话,Vivado默认都会分析的,这样…

赞同 7

1 条评论

对于Xilinx的FPGA,每一片都有一个专门的ID,就像我们的身份证号一样,每个都不一样,Xilinx也形象的把这个ID叫做DNA。7系列以及之前FPGA的DNA有57bit,Ultrascal…

赞同 4

添加评论

本篇文章要写的是调试Xilinx网络IP时踩到的一个坑,也是控制PHY芯片时的一个坑,板卡上的PHY芯片是非常经典的88E1111,使用MDIO接口控制。 本身MDIO接口的时序也不是很难,非常…

赞同 3

3 条评论

管脚约束问题导致生成bit时报错 如何在不重新Implentation情况下生成bit?

在FPGA开发中,我们经常遇到因为管脚忘记约束,导致最后生成bit的时候报错 1.管脚电平未约束 像上面这个图中,由于在约束中忘记指定mdc和mdio的电平,再经过了长时间的综合和实现后,最后的Gen…

赞同 7

1 条评论

笔者之前写过一篇文章 生成Verilog HDL例化模板,在这边文章中,使用Python来完成Verilog的例化。但其实Vs Code也有类似功能,操作也比较方便。 还是要安装Python,并添加…

赞同 5

添加评论

什么是ECO?ECO 指的是Engineering Change Order,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 的叫法算…

赞同 11

添加评论

首先需要明确的一点是,他们都是高速收发器,只是传输速率同,速率大小为: GTP < GPX < GTH < GTZ < GTY < GTM 不同芯片上使用的高速收发器也不同,而且同样是GTX,不同系列芯片上的速率也可能不同。 比如7系列的FPGA,GTP最高可以达到6.6Gb/s,…

赞同 5

1 条评论

Vivado IP中的Shared Logic到底是干嘛的?

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面: 可能很多同学并没有很关注这个页面,直接默认设置就完事了。 但其实这…

赞同 11

1 条评论

Vivado的Implementation主要有三大步: opt_design,会生成opt_desgin.dcp place_design,会生成place_design.dcp route_design…

赞同 9

添加评论

今天我们来研究一下D触发器都有哪几种类型?又对应什么样的代码? 在Xilinx的FPGA中,D触发器是下面这个样子: 其中,D是数据输入端口,CE是使能端口,CLK是时钟输入,SR是Set/Res…

赞同 8

添加评论

背景: FPGA型号:Ultrasacle xcku060 DDR型号:MT40A512M16HA 板卡用的一直好好的,硬件没有什么问题,DDR跑在2400M,也一直正常工作。 但最近有个工程中,需要增加SRIO接口,SRIO接收的数据需要先过DDR,工程编完下载bit后,偶尔会提示DDR初始化失败: 分析如下: 板卡用了很久,D…

赞同 4

4 条评论

本文整理自高亚军老师的Vivado HLS视频教程 1. HLS新的数据类型 C/C++数据类型: 其中HLS中不支持char16_t和char32_t两种数据类型。在C/C++中,所有的数…

赞同 13

添加评论

首先,从理论上讲,Hold Time违例,是因为时钟绕的太远,到达时间太晚。而且综合之后给出的时序报告都是估计值,因此综合之后可以不考虑Hold Time,只考虑Setup Time;即便此时Ho…

赞同 16

2 条评论

Vivado时序收敛技术(二) 时序违例的根本原因及解决方法

本文整理自Xilinx公开课:Vivado时序收敛技术。 有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。 有很多内容也在我的时序约束课程中讲到过,都是免费课程,大家可以在我的知…

赞同 27

2 条评论

本文整理自Xilinx公开课:Vivado时序收敛技术。 有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。 有很多内容也在我的时序约束课程中讲到过,都是免费课程,大家可以在我的知…

赞同 31

2 条评论

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。 当然现在Xil…

赞同 62

4 条评论

Xilinx FPGA Partial Reconfiguration 部分重配置 详细教程

Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。 这里我们使用的Vivado版本是…

赞同 51

12 条评论

我们完成Vivado的工程后,大部分情况不能把整个工程的源代码都直接给客户或者其他工程师,需要我们先进行一些封装后再给他们,就像软件代码中会编译成dll后再Release给别人。 在Vivado…

赞同 22

1 条评论

Vivado中jobs和threads的区别?选择多个jobs能加快实现速度么?

在用Vivado对工程编译时,会弹出下面的对话框: 备注:虽然FPGA不能叫编译,但很多工程师为了方便起见,将综合+实现+生成bit文件的过程统称为编译了,这种说法大家理解就好。 很多工程师都会选择多…

赞同 22

2 条评论

本篇文章参考Xilinx White Paper: Get Smart About Reset: Think Local, Not Global 在没看这篇文章前,回想一下平时我们常用的复位方式:…

赞同 35

4 条评论

git有多好用我就不用多说了,可谓是程序员必备技能之一。对于一般的软件代码来说,只需把源文件进行git管理即可。但对于FPGA工程师来说,使用git多多少少有些蛋疼,主要有下面几个问题: 有bd文件…

赞同 36

1 条评论

大家一致避免使用的锁存器为什么依然存在于FPGA中?我们对锁存器有什么误解?

前言 在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数…

赞同 127

16 条评论

影响FPGA时序的进位链(Carry Chain), 你用对了么?

在FPGA中我们写的最多的逻辑是什么?相信对大部分朋友来说应该都是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到…

赞同 45

13 条评论

之前我写过一篇过于vivado生成HDL例化模板的文章。 但实际使用起来,发现很不好用,每次都要先点击’Open Elaborated Design’后才能使用(很慢),而且生成的例化模板接口顺序也…

赞同 17

3 条评论

张大侠 62 人赞同了该文章

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。

当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多。但我们大多数的工程还是无法避免使用HDL来连接两个module。所以本文就推荐使用SystemVerilog来简化FPGA中接口的连接方式。

也许很多FPGA工程师对SystemVerilog并不是很了解,因为以前的FPGA开发工具是不支持SystemVerilog的,导致大家都是用VHDL或者Verilog来开发,但现在Vivado对SystemVerilog的支持已经比较好了,完全可以使用SystemVerilog写出可综合的FPGA程序,而且FPGA开发中只会使用的SystemVerilog语法的一小部分,入门也很快,因此建议FPGA工程师学一下SystemVerilog。

本文中用到的logic关键字的解释可以参考SystemVerilog教程之数据类型1

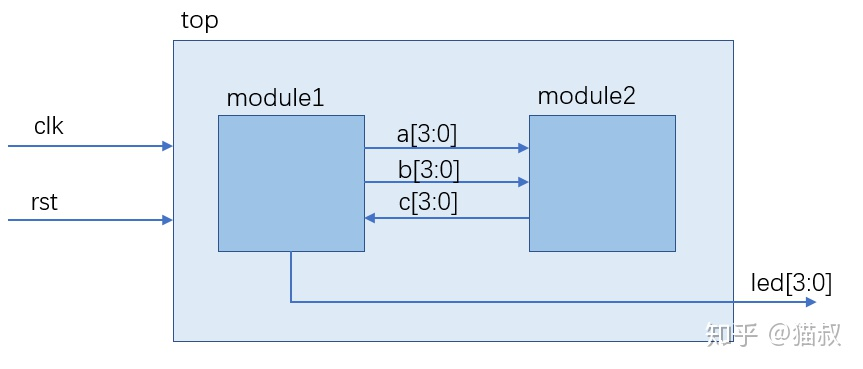

此次例程也比较简单,有两个模块module1和module2,module1中输出a和b,在module2中完成加法后再返还给module1,最终输出的led=c | a。

首先用Verilog来实现,代码也比较简单,就简单解释一句:文件格式都是.sv,这是因为SystemVerilog的语法都是包含Verilog的。

//top.sv

module top(

input clk,

input rst,

output [3:0] led

);

logic [3:0] a ;

logic [3:0] b ;

logic [3:0] c ;

module1 inst_module1(

.clk (clk ),

.rst (rst ),

.a (a),

.b (b),

.c (c),

.led (led)

);

module2 inst_module2(

.clk (clk ),

.rst (rst ),

.a (a),

.b (b),

.c (c)

);

endmodule

// module1.sv

module module1(

input clk,

input rst,

output logic [3:0] a,

output logic [3:0] b,

input logic [3:0] c,

output logic [3:0] led

);

assign led = c | a;

always @ ( posedge clk ) begin

if(rst) begin

a <= 4'd1;

b <= 4'd2;

end

else begin

a <= a + 1'b1;

b <= b + 1'b1;

end

end

endmodule

// module2.sv

module module2(

input clk,

input rst,

input logic [3:0] a,

input logic [3:0] b,

output logic [3:0] c

);

always @ ( posedge clk ) begin

if(rst)

c <= 4'd1;

else

c <= a + b;

end

endmodule

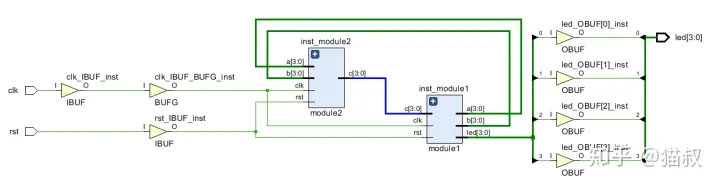

综合之后的Schematic如下图所示:(为了更好的表示电路结构,我将flatten_hierarchy选为了none)

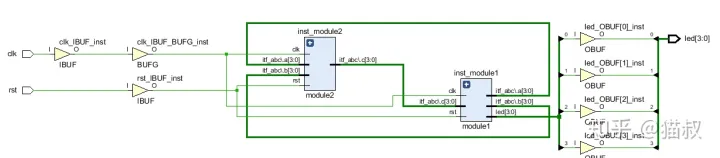

下面我们把程序稍作改动,将a/b/c三个接口使用SystemVerilog中的interface来连接。

在工程中添加my_itf.sv文件如下:

// my_itf.sv

interface my_itf;

logic [3:0] a, b, c;

modport mod1 (input c, output a, b);

modport mod2 (input a, b, output c );

endinterface : my_itf

关键字interface就表示要创建一个接口模块,里面包含了3个接口:a/b/c。

modport定义了这三个接口的方向,对于module1来说,a和b是输出,c是输入;对于module2来说,a和b是输入,c是输出。

注:也可以不使用modport,Vivado会根据代码自动推断出接口的方向,但不建议这么做

修改module1.sv如下,其中a/b/c端口换成了my_itf.mod1 itf_abc,my_itf.mod1就表示my_itf接口的方向按照mod1中指定的,而且代码中的a、b、c要相应的换成itf_abc.a、itf_abc.b、itf_abc.c.

// module1.sv

module module1(

input clk,

input rst,

my_itf.mod1 itf_abc,

output logic [3:0] led

);

assign led = itf_abc.c | itf_abc.a;

always @ ( posedge clk ) begin

if(rst) begin

itf_abc.a <= 4'd1;

itf_abc.b <= 4'd2;

end

else begin

itf_abc.a <= itf_abc.a + 1'b1;

itf_abc.b <= itf_abc.b + 1'b1;

end

end

endmodule

修改module2.sv代码如下,原则跟上面是一样的,不再赘述。

// module2.sv

module module2(

input clk,

input rst,

my_itf.mod2 itf_abc

);

always @ ( posedge clk ) begin

if(rst)

itf_abc.c <= 4'd1;

else

itf_abc.c <= itf_abc.a + itf_abc.b;

end

endmodule

修改top.sv如下,例化my_itf接口,将itf_abc.mod1传给module1,将itf_abc.mod2传给module2.

// top.sv

module top(

input clk,

input rst,

output [3:0] led

);

logic [3:0] a ;

logic [3:0] b ;

logic [3:0] c ;

my_itf itf_abc();

module1 inst_module1(

.clk (clk ),

.rst (rst ),

.itf_abc (itf_abc.mod1),

.led (led)

);

module2 inst_module2(

.clk (clk ),

.rst (rst ),

.itf_abc (itf_abc.mod2)

);

endmodule

大功告成!!!

综合后Schematic如下,跟上面的图只是名字不同,电路是一样的。

微信公众号:Quant_Times

FPGA技术交流群加微信:xhclsys2

发布于 2020-07-20 23:48

此处可能存在不合适展示的内容,页面不予展示。您可通过相关编辑功能自查并修改。

如您确认内容无涉及 不当用语 / 纯广告导流 / 暴力 / 低俗色情 / 侵权 / 盗版 / 虚假 / 无价值内容或违法国家有关法律法规的内容,可点击提交进行申诉,我们将尽快为您处理。